ĪĪĪĪĄ┌69 ī├ IEEE ć°ļHļŖūėįOéõ─ĻĢ■īóė┌ 12 į┬ 9 ╚šķ_─╗Ż¼Ģ■ūhŅAĖµŲ¼’@╩ŠŻ¼čąŠ┐╚╦åTę╗ų▒į┌öUš╣ČÓĒŚ╝╝ągĄ─┬ĘŠĆłDŻ¼╠žäe╩Ū─Ūą®ė├ė┌ųŲįņCPU║═GPU Ą─╝╝ągĪŻ

ĪĪĪĪė╔ė┌ąŠŲ¼╣½╦Š¤oĘ©═©▀^į┌Č■ŠS╔Ž┐sąĪąŠŲ¼╣”─▄üĒ└^└mį÷╝ėŠ¦¾w╣▄├▄Č╚Ż¼ę“┤╦╦¹éā═©▀^īóąŠŲ¼Čč»Bį┌ę╗Ų▀M╚ļ┴╦╚²ŠSĪŻ¼Fį┌╦¹éāš²ų┬┴”ė┌į┌▀@ą®ąŠŲ¼ųąśŗĮ©Š¦¾w╣▄ĪŻĮėŽ┬üĒŻ¼╦¹éā║▄┐╔─▄Ģ■═©▀^╩╣ė├Č■┴“╗»ŃfĄ╚2D ░ļī¦¾wįOėŗ 3D ļŖ┬ĘŻ¼▀Mę╗▓Į▀M╚ļ╚²ŠSŅIė“ĪŻ╦∙ėą▀@ą®╝╝ągČ╝┐╔─▄Ę■äšė┌ÖCŲ„īW┴ĢŻ¼▀@╩Ūę╗ĘNī”╠Ä└Ē─▄┴”╚šęµį÷ķLĄ─ąĶŪ¾Ą─æ¬ė├│╠ą“ĪŻĄ½ IEDM ╔Ž░l▒ĒĄ─Ųõ╦¹čąŠ┐▒Ē├„Ż¼3D ╣Ķ║═ 2D░ļī¦¾w▓ó▓╗╩Ū*─▄ūī╔±ĮøŠWĮj▒Ż│ųš²│Ż▀\▐DĄ─¢|╬„ĪŻ

ĪĪĪĪ3DąŠŲ¼Čč»B

ĪĪĪĪ═©▀^Čč»BąŠŲ¼(į┌▒Š└²ųąĘQ×ķąĪąŠŲ¼(Chiplet))üĒį÷╝ė┐╔ęįöD╚ļĮoČ©ģ^ė“Ą─Š¦¾w╣▄öĄ┴┐Ż¼▀@╝╚╩Ū╣ĶĄ─¼Fį┌Ż¼ę▓╩Ū╬┤üĒĪŻę╗░ŃüĒšfŻ¼ųŲįņ╔╠š²į┌┼¼┴”į÷╝ėąŠŲ¼ų«ķgĄ─┤╣ų▒▀BĮėĄ─├▄Č╚ĪŻĄ½ę▓ėąę╗ą®▓ó░l░YĪŻ

ĪĪĪĪę╗╩ŪĖ─ūā┴╦ąŠŲ¼╗ź▀Būė╝»Ą─▓╝ŠųĪŻÅ─ 2024 ─Ļ─®ķ_╩╝Ż¼ąŠŲ¼ųŲįņ╔╠īóķ_╩╝į┌╣ĶŽ┬ĘĮśŗĮ©ļŖ┴”é„▌ö╗ź▀BŻ¼Č°īóöĄō■╗ź▀B┴¶į┌╔ŽĘĮĪŻ▀@ĘN▒╗ĘQ×ķ“▒│├µ╣®ļŖ”Ą─ĘĮ░ĖĢ■ĦüĒąŠŲ¼╣½╦Šš²į┌蹊┐Ą─Ė„ĘN║¾╣¹ĪŻ┐┤üĒėó╠žĀ¢īóį┌▒Šī├Ą─IEDMėæšō▒│├µļŖį┤ī” 3D įOéõĄ─ė░ĒæĪŻIMEC īó蹊┐ĘQ×ķŽĄĮy╝╝ągģf═¼ā×╗» (STCO)Ą─ 3D ąŠŲ¼įOėŗ└Ē─ŅĄ─ė░ĒæĪŻ(▀@éĆŽļĘ©╩ŪŻ¼╬┤üĒĄ─╠Ä└ĒŲ„īó▒╗ĘųĮŌ×ķ╗∙▒Š╣”─▄Ż¼├┐éĆ╣”─▄Č╝īó╬╗ė┌Ųõūį╝║Ą─ąĪąŠŲ¼╔ŽŻ¼▀@ą®ąĪąŠŲ¼īó▓╔ė├▀m║Žįō╣żū„Ą─*╝╝ągųŲ│╔Ż¼╚╗║¾▀@ą®ąĪąŠŲ¼īó▒╗ųžą┬ĮMčb│╔ę╗éĆŽĄĮy╩╣ė├ 3D Čč»B║═Ųõ╦¹Ž╚▀MĘŌčb╝╝ągĪŻ)═¼ĢrŻ¼┼_ĘeļŖīóĮŌøQ 3D ąŠŲ¼Čč»BųąķLŲ┌┤µį┌Ą─å¢Ņ}——╚ń║╬Å─ĮM║ŽąŠŲ¼ųą┼┼│÷¤ß┴┐ĪŻ

ĪĪĪĪŅÖ├¹╦╝┴xŻ¼╦∙ų^3DąŠŲ¼Čč»BŻ¼╩Ūīóę╗éĆ═Ļš¹Ą─ėŗ╦ŃÖCąŠŲ¼(└²╚ń DRAM)Ę┼ų├į┌┴Ēę╗éĆąŠŲ¼(CPU)ų«╔ŽĪŻĮY╣¹Ż¼ļŖ┬Ę░Õ╔ŽįŁ▒ŠŽÓŠÓÄū└Õ├ūĄ─ā╔éĆąŠŲ¼¼Fį┌ŽÓŠÓ▓╗ĄĮę╗║┴├ūĪŻ▀@ĮĄĄ═┴╦╣”║─(═©▀^Ń~ŠĆé„▌ööĄō■╩Ūę╗╝■║▄┬ķ¤®Ą─╩┬Ūķ)Ż¼▓óŪę▀Ć┤¾┤¾╠ßĖ▀┴╦ĦīÆĪŻ

ĪĪĪĪIEEEę▓▒Ē╩ŠŻ¼«öŪ░├┐ę╗┤·╠Ä└ĒŲ„Ą─ąį─▄Č╝ąĶę¬▒╚╔Žę╗┤·Ė³║├Ż¼Å─ūŅ╗∙▒ŠĄ─ĮŪČ╚üĒšfŻ¼▀@ęŌ╬Čų°īóĖ³ČÓĄ─▀ē▌ŗ╝»│╔ĄĮ╣ĶŲ¼╔ŽĪŻĄ½┤µį┌ā╔éĆå¢Ņ}Ż║ę╗╩Ū╬ęéā┐sąĪŠ¦¾w╣▄╝░ŲõĮM│╔Ą─▀ē▌ŗ║═┤µā”ēKĄ──▄┴”š²į┌Ę┼ŠÅĪŻ┴Ēę╗éĆ╩ŪąŠŲ¼ęčĮø▀_ĄĮ┴╦│▀┤ńśOŽ▐Ż¼ę“×ķ╣Ō┐╠╣żŠ▀ų╗─▄į┌╝s 850 ŲĮĘĮ║┴├ūĄ─ģ^ė“╔Žą╬│╔łD░ĖĪŻ

ĪĪĪĪ×ķ┴╦ĮŌøQ▀@ą®å¢Ņ}Ż¼Äū─ĻüĒŻ¼Ų¼╔ŽŽĄĮyķ_░l╚╦åTęčĮøķ_╩╝īóŲõĖ³┤¾Ą─įOėŗĘųĮŌ×ķĖ³ąĪĄ─ąĪąŠŲ¼Ż¼▓óīó╦³éāį┌═¼ę╗ĘŌčbā╚▀BĮėį┌ę╗ŲŻ¼ęįėąą¦į÷╝ė╣Ķ├µĘeĄ╚ā×ä▌ĪŻį┌ CPU ųąŻ¼▀@ą®µ£Įė┤¾ČÓ╩Ū╦∙ų^Ą─ 2.5DŻ¼ŲõųąąĪąŠŲ¼▒╦┤╦ŽÓÓÅįOų├Ż¼▓ó╩╣ė├Č╠Č°├▄╝»Ą─╗ź▀B▀Mąą▀BĮėĪŻ╝╚╚╗┤¾ČÓöĄų„ę¬ųŲįņ╔╠ęčĮøŠ═ 2.5D ąĪąŠŲ¼ĄĮąĪąŠŲ¼═©ą┼ś╦£╩▀_│╔ę╗ų┬Ż¼▀@ĘNŅÉą═Ą─╝»│╔Ą─ä▌Ņ^┐╔─▄ų╗Ģ■į÷ķLĪŻ

ĪĪĪĪĄ½ę¬Ž±į┌═¼ę╗ąŠŲ¼╔Žę╗śėé„▌öšµš²┤¾┴┐Ą─öĄō■Ż¼─·ąĶę¬Ė³Č╠ĪóĖ³├▄╝»Ą─▀BĮėŻ¼Č°▀@ų╗─▄═©▀^īóę╗éĆąŠŲ¼Čč»Bį┌┴Ēę╗éĆąŠŲ¼╔ŽüĒīŹ¼FĪŻ├µī”├µ▀BĮėā╔éĆąŠŲ¼ęŌ╬Čų°├┐ŲĮĘĮ║┴├ūę¬Į©┴óöĄŪ¦éĆ▀BĮėĪŻ▀@ę▓┤▀╔·┴╦3DąŠŲ¼Čč»BĪŻ

ĪĪĪĪSynopsysį┌ę╗Ų¬▓®┐═╬─š┬ųąųĖ│÷Ż¼Čč»BąŠŲ¼ų«ķgĄ─öĄō■é„▌ö═©▀^╝»│╔į┌Ąū▓┐ąŠŲ¼ųąĄ─ TSV ▀MąąĪŻ▀@ą® TSV ╩Ū┤╣ų▒▀\ąąĄ─╬’└Ēų∙Ż¼ė╔Ń~Ą╚ī¦ļŖ▓─┴ŽųŲ│╔ĪŻīóČč»BąŠŲ¼š│║ŽĄĮå╬éĆĘŌčbųąČ°▓╗╩Ū PCB ╔ŽĄ─ČÓéĆĘŌčbųąŻ¼┐╔īó I/O ├▄Č╚╠ßĖ▀ 100 ▒ČĪŻ▓╔ė├*Ż¼├┐▒╚╠žé„▌ö─▄┴┐┐╔ĮĄĄ═ų┴ 30 ▒ČĪŻ

ĪĪĪĪų┴ė┌▒│├µ╣®ļŖŻ¼░┤ššIEEE╦∙šfŻ¼Ž“öĄ╩«ā|éĆŠ¦¾w╣▄╠ß╣®ļŖ┴„š²čĖ╦┘│╔×ķĖ▀ąį─▄ SoC įOėŗĄ─ų„ę¬Ų┐Ņių«ę╗ĪŻļSų°Š¦¾w╣▄▓╗öÓūāĄ├įĮüĒįĮąĪŻ¼×ķŠ¦¾w╣▄╠ß╣®ļŖ┴„Ą─╗ź▀BŠĆ▒žĒÜ┼┼┴ąĄ├Ė³Šo├▄ĪóĖ³Š½╝ÜŻ¼▀@Ģ■į÷╝ėļŖūĶ▓óŽ¹║─╣”┬╩ĪŻ▀@ĘNŪķør▓╗─▄į┘└^└mŽ┬╚źŻ║╚ń╣¹ļŖūė▀M│÷ąŠŲ¼╔ŽĄ─įOéõĄ─ĘĮ╩Įø]ėą░l╔·ųž┤¾ūā╗»Ż¼╬ęéāī󊦾w╣▄ųŲįņĄ├į┘ąĪę▓¤oØ·ė┌╩┬ĪŻ

ĪĪĪĪį┌«öĮ±Ą─╠Ä└ĒŲ„ųąŻ¼ą┼╠¢║═╣”┬╩Č╝Å─╔ŽĘĮĄĮ▀_╣Ķ[£\╗ę╔½]ĪŻą┬╝╝ągīóĘųļx▀@ą®╣”─▄Ż¼Å─Č°╣Ø╩ĪļŖ┴”▓ó×ķą┼╠¢┬ĘŠĆ“v│÷Ė³ČÓ┐šķg[ėę]ĪŻ

ĪĪĪĪąę▀\Ą─╩ŪŻ¼╬ęéāėąę╗éĆėąŪ░═ŠĄ─ĮŌøQĘĮ░ĖŻ║╬ęéā┐╔ęį╩╣ė├ķLŲ┌ęįüĒ▒╗║÷ęĢĄ─╣ĶĄ─ę╗├µĪŻ

ĪĪĪĪ×ķ┴╦Å─ SoC ½@╚ĪļŖį┤║═ą┼╠¢Ż¼╬ęéā═©│ŻīóūŅ╔ŽīėĮī┘(ŠÓļxŠ¦¾w╣▄ūŅ▀h)▀BĮėĄĮąŠŲ¼ĘŌčbųąĄ─║ĖŪ“(ę▓ĘQ×ķ═╣³c)ĪŻę“┤╦Ż¼×ķ┴╦ūīļŖūėĄĮ▀_╚╬║╬Š¦¾w╣▄ęį═Ļ│╔ėąė├Ą─╣żū„Ż¼╦³éā▒žĒÜ┤®▀^ 10 ĄĮ 20 īėįĮüĒįĮšŁ║═Ū·š█Ą─Įī┘Ż¼ų▒ĄĮ╦³éāūŅĮK─▄ē“öDĄĮūŅ║¾ę╗īėŠų▓┐ī¦ŠĆĪŻ▀@ĘNĘų┼õļŖ┴”Ą─ĘĮ╩ĮÅ─Ė∙▒Š╔ŽüĒšf╩Ūėąōp║─Ą─ĪŻė┌╩ŪŻ¼╬ęéā└¹ė├Š¦¾w╣▄Ž┬ĘĮĄ─“┐š”╣ĶŻ¼▀@š²╩Ūimecķ_äōĄ─ę╗ĘNĘQ×ķ“┬±╚ļ╩ĮļŖį┤▄ē”╗“ BPR Ą─ųŲįņĖ┼─ŅĪŻįō╝╝ągį┌Š¦¾w╣▄Ž┬ĘĮČ°▓╗╩Ū╔ŽĘĮĮ©┴óļŖį┤▀BĮėŻ¼─┐Ą─╩ŪäōĮ©Ė³┤ųĪóļŖūĶĖ³ąĪĄ─ļŖį┤▄ēŻ¼▓ó×ķŠ¦¾w╣▄īė╔ŽĘĮĄ─ą┼╠¢│ą▌d╗ź▀BßīĘ┼┐šķgĪŻ

ĪĪĪĪCFET ║═ 3D ļŖ┬Ę

ĪĪĪĪļSų°Ž╚▀MąŠŲ¼Ą─*ųŲįņ╔╠▐DŽ“─│ĘNą╬╩ĮĄ─╝{├ūŲ¼(╗“Łh¢┼)Š¦¾w╣▄Ż¼ī”║¾└mŲ„╝■——å╬Ų¼╗źčał÷ą¦æ¬Š¦¾w╣▄(CFET)Ą─蹊┐▓╗öÓ╝ėÅŖĪŻ

ĪĪĪĪCFET Ą─ŽļĘ©╩Ūė╔ IMEC 蹊┐ÖCśŗį┌ 2018 ─Ļ╠ß│÷Ż¼Ųõųą n ą═║═ p ą═Š¦¾w╣▄┤╣ų▒å╬Ų¼Čč»B(ģóęŖ IMEC ╠ß│÷Ą─“ n-over-p”╗źča FET ╠ß░Ė)ĪŻ┤╦║¾Ż¼┤¾┴┐蹊┐šō╬─│õīŹ┴╦įō╠ß░ĖŻ¼Ą½▀@ą®šō╬─üĒūį IMEC ║═īWąg蹊┐╚╦åTŻ¼Č°▓╗╩Ū╔╠śIĮM┐ŚĄ─čą░lłFĻĀĪŻ

ĪĪĪĪCFET Ą─├„’@ā×ä▌╩Ūā╔éĆŠ¦¾w╣▄š╝ō■ GAAĪóFinFET ╗“ŲĮ├µ╝▄śŗųąę╗éĆŠ¦¾w╣▄Ą─┐šķgĪŻĄ½▀@ę▓ęŌ╬Čų°┐╔ęįĖ³ėąą¦ĄžįOėŗ CMOS ▀ē▌ŗļŖ┬ĘĪŻIMEC ┤╦Ū░į°ųĖ│÷Ż¼ś╦£╩å╬į¬├µĘeų„ę¬╚ĪøQė┌ī”Š¦¾w╣▄Č╦ūėĄ─įLå¢Ż¼Č° CFET ┐╔ęį║å╗»▀@ę╗³cĪŻ

ĪĪĪĪį┌ IEDM ╔ŽŻ¼┼_ĘeļŖīóš╣╩ŠŲõį┌ CFET ĘĮ├µĄ─┼¼┴”ĪŻ╦¹éā┬ĢĘQ┴╝┬╩ėą╦∙╠ßĖ▀(╝┤ 300 ║┴├ū╣ĶŠ¦łA╔Ž╣żū„Ų„╝■Ą─▒╚└²)Ż¼▓óŪęīóĮM║ŽŲ„╝■┐sąĪĄĮ▒╚ų«Ū░č▌╩ŠĄ─Ė³īŹė├Ą─│▀┤ńĪŻ

ĪĪĪĪį┌ūŅą┬Ą─ą┬┬äšō╬─ųąŻ¼┼_ĘeļŖ蹊┐╚╦åTīó═Ų│÷┴╦╦¹éā╦∙ų^Ą─īŹė├Ą─å╬Ų¼ CFET ╝▄śŗĘĮĘ©Ż¼ė├ė┌▀ē▌ŗ╝╝ągöUš╣ĪŻ╦³▓╔ė├ 48nm ¢┼śOķgŠÓČč»B╩Į n-FET-on-p-FET ╣Ķ╝{├ūŲ¼Š¦¾w╣▄ĪŻ▀@ą®▒Ē¼F│÷Ė▀═©æBļŖ┴„/Ą═üåķōųĄą╣┬®Ż¼Å─Č°«a╔·┴Ņ╚╦ėĪŽ¾╔Ņ┐╠Ą─ķ_/ĻPļŖ┴„▒╚(┴∙éĆöĄ┴┐╝ē)ĪŻ╦¹éā▀Ć▒Ē¼F│÷ŽÓī”▌^Ė▀Ą─┴╝┬╩Ż¼FET ┤µ╗Ņ┬╩ >90%ĪŻ▒M╣▄ų«Ū░Ą─╣żū„▒Ē├„╣”─▄ąį CFET Ų„╝■┐╔ęįį┌ 300mm Š¦łA╔ŽśŗĮ©Ż¼Ą½▀@ą®Ų„╝■Ą─¢┼śOķgŠÓī”ė┌╬┤üĒĄ─öUš╣üĒšf╠½┤¾┴╦ĪŻį┌▀@ĒŚ╣żū„ųąŻ¼═©▀^┤╣ų▒Čč»BĄ─ n/p į┤śO-┬®śO (SD) ═ŌčėīŹ¼F┴╦Ė³ŽÓĻPĄ─ 48nm ¢┼śOķgŠÓŻ¼Ųõųą░³└©ųąķgļŖĮķ┘|Ė¶ļxĪóē|Ų¼║═ n/p SD Ė¶ļxĪŻļm╚╗╚į▒žĒÜ╝»│╔Ųõ╦¹╗∙▒Š╣”─▄▓┼─▄ßīĘ┼ CFET ╝╝ągĄ─Øō┴”Ż¼Ą½▀@ĒŚ╣żū„×ķīŹ¼F▀@ę╗─┐ś╦õüŲĮ┴╦Ą└┬ĘĪŻ

ĪĪĪĪ╔ŽłD’@╩Š┴╦Ų„╝■╝▄śŗÅ─ FinFET ĄĮ╝{├ūŲ¼ FET (NSFET) į┘ĄĮ 3D Čč»B╩Į CFETĄ─č▌ūāŻ¼ą┬ĘfĄ─Š¦¾w╣▄╝▄śŗäōą┬▓╗öÓ═Ųäė─”Ā¢Č©┬╔Ą─čė└m;Ąū▓┐╩Ūå╬Ų¼ CFET Ą─ā╚┬ōÖMĮž├µ TEM č▌╩ŠŻ¼¢┼śOķgŠÓ×ķ48nmŻ¼nFET Ę┼ų├į┌ pFET ╔ŽĘĮŻ¼ā╔ĘNŅÉą═Ą─Š¦¾w╣▄Č╝▒╗å╬ę╗mental gate░³ć·ĪŻ

ĪĪĪĪ┼c┤╦═¼ĢrŻ¼ėó╠žĀ¢čąŠ┐╚╦åTīóįö╝ÜĮķĮBė╔å╬éĆ CFET śŗĮ©Ą─inverter circuit ĪŻ▀@ĘNļŖ┬ĘĄ─│▀┤ń┐╔─▄ų╗ėąŲš═© CMOS ļŖ┬ĘĄ─ę╗░ļĪŻėó╠žĀ¢▀ĆīóĮŌßīę╗ĘNą┬ĘĮ░ĖŻ¼ė├ė┌╔·«a NMOS ║═ PMOS ▓┐ĘųŠ▀ėą▓╗═¼öĄ┴┐╝{├ūŲ¼Ą─ CFETĪŻ

ĪĪĪĪėó╠žĀ¢▒Ē╩ŠŻ¼įōŲ„╝■ė╔ 3p-FET ╝{├ūĦĒö▓┐Ą─ 3 éĆ n-FET ╝{├ūĦĮM│╔Ż¼╦³éāų«ķgĄ─┤╣ų▒ķgŠÓ×ķ 30 ╝{├ūĪŻ╦¹éā╩╣ė├įōŲ„╝■ęį 60nm ¢┼śOķgŠÓśŗĮ©╚½╣”─▄inverters (test circuits)Ż¼▀@į┌śIĮń╔ąī┘╩ū┤╬ĪŻįōŲ„╝■▀Ć▓╔ė├┤╣ų▒Čč»Bļp S/D ═Ōčė╝╝ąg;▀BĮė n ║═ p Š¦¾w╣▄Ą─ļpĮī┘╣”║»öĄ¢┼śO»Bīė;ęį╝░┼c▒│├µ╣®ļŖ║═ų▒Įė▒│├µŲ„╝■Įėė|Ą─╝»│╔ĪŻčąŠ┐╚╦åT▀Ćīó├Ķ╩÷╝{├ūĦ“depopulation”▀^│╠Ż¼ė├ė┌ąĶę¬öĄ┴┐▓╗Ą╚Ą─ n-MOS/p-MOS Ų„╝■ĪŻ▀@ĒŚ╣żū„ėąų·ė┌╝ė╔Ņī”▀ē▌ŗ║═ SRAM æ¬ė├öUš╣ CFET Øō┴”Ą─└ĒĮŌŻ¼▓ó┴╦ĮŌĻPµIĄ─╣ż╦ć═Ųäėę“╦žĪŻ

ĪĪĪĪ╚ń╔ŽłD╦∙╩ŠŻ¼łD(a) ╩Ū CPP=60nm ┤╣ų▒Čč»Bļpį┤śO-┬®śO (SDŻ║source-drain) ═Ōčė║¾ CFET Ų„╝■Ą─ TEM ’@╬óššŲ¼;łD(b) ╩Ūį┌ CPP=60nm Ž┬ŽÓ═¼öU╔óĄ─ CFET Ų„╝■į┌ VDS=0.05V ║═ 0.65V ĢrĄ─ ID-VG Ū·ŠĆĪŻĄū▓┐ p-MOS ═©▀^▒│├µŲ„╝■ė|³c (BSCONŻ║backside device contacts) ▀Mąą£y┴┐Ż¼Č°Ēö▓┐ n-MOS ═©▀^£\š²├µė|³c║═▒│├µļŖį┤═©┐ū▀Mąą£y┴┐ĪŻī”ė┌ n-MOS ║═ p-MOSŻ¼Ų„╝■Ą─üåķōųĄö[Ę∙ (SS) Ęųäe×ķ 63mV/dec ║═ 66mV/decŻ¼DIBL Ęųäe×ķ 57mV/V ║═ 38mV/V;łD(c) ╩Ū─µūāŲ„ļŖē║é„▌öŪ·ŠĆŻ¼╦³“×ūC┴╦╦∙ėą═╗│÷’@╩ŠĄ─ĮM╝■Č╝į┌═¼ę╗öU╔ó╔Žę╗Ų╣żū„Ż¼Å─Č°īŹ¼F┴╦ŲĮ║Ō┴╝║├Ą─invertersĪŻ

ĪĪĪĪ2DŠ¦¾w╣▄

ĪĪĪĪ┐sąĪ╝{├ūŲ¼Š¦¾w╣▄(ęį╝░ CFET)Ą─│▀┤ńīóęŌ╬Čų°Š¦¾w╣▄║╦ą─Ą─╣ĶĦ( ribbons of silicon)ūāĄ├įĮüĒįĮ▒ĪĪŻūŅĮKŻ¼īóø]ėąūŃē“Ą─╣ĶįŁūėüĒ═Ļ│╔▀@ĒŚ╣żū„ĪŻę“┤╦Ż¼čąŠ┐╚╦åTš²į┌▐DŽ“Č■ŠS░ļī¦¾w▓─┴ŽŻ¼╝┤╩╣╩Ūę╗īėų╗ėąę╗éĆįŁūė║±Ą─▓─┴ŽĪŻ

ĪĪĪĪČ■ŠS░ļī¦¾wī┘ė┌ę╗ŅÉĘQ×ķ▀^Č╔Įī┘Č■┴“ī┘╗»╬’Ą─▓─┴ŽĪŻŲõųąŻ¼čąŠ┐*Ą─╩ŪČ■┴“╗»ŃfĪŻ└Ēšō╔ŽŻ¼ļŖūėæ¬įō▒╚MoS2Ė³┐ņĄž┤®▀^Č■┴“╗»µu(┴Ēę╗ĘNČ■ŠS▓─┴Ž)ĪŻ

ĪĪĪĪ═¼ĢrŻ¼Č■ŠS░ļī¦¾w┐╔ęį╚Ī┤·╣ĶĄ─ŽļĘ©├µ┼Rų°╚²éĆå¢Ņ}ĪŻę╗╩Ū╔·«a(╗“▐DęŲ)¤o╚▒Ž▌Ą─Č■ŠS░ļī¦¾wīėĘŪ│Ż└¦ļyĪŻĄ┌Č■éĆå¢Ņ}╩ŪŠ¦¾w╣▄ė|³c║═Č■ŠS░ļī¦¾wų«ķgĄ─ļŖūĶ╠½Ė▀ĪŻūŅ║¾Ż¼ī”ė┌ CMOSŻ¼─·ąĶę¬ę╗ĘN─▄ē“═¼śė┴╝║├Ąžé„ī¦┐šč©║═ļŖūėĄ─░ļī¦¾wŻ¼Ą½╦Ų║§ø]ėąę╗ĘNČ■ŠS░ļī¦¾w─▄ē“═¼Ģré„ī¦┐šč©║═ļŖūėĪŻ

ĪĪĪĪō■IEEEĄ─ł¾Ą└Ż¼Č■ŠS░ļī¦¾w├µ┼RĄ─*šŽĄK╩Ū┼c╦³éā▀MąąĄ═ļŖūĶ▀BĮėĪŻįōå¢Ņ}▒╗ĘQ×ķ“Fermi-level pinning”Ż¼╦³Ą─ęŌ╦╝╩ŪĮī┘ė|³c║═░ļī¦¾wĄ─ļŖūė─▄┴┐ų«ķgĄ─▓╗Ųź┼õĢ■ī”ļŖ┴„«a╔·Ė▀ūĶä▌ēŠ(high-resistance barrier)ĪŻ▀@ĘNąż╠ž╗∙ä▌ēŠ()Ą─«a╔·╩Ūę“×ķĮń├µĖĮĮ³Ą─ļŖūė┴„╚ļ▌^Ą═─▄┴┐Ą─▓─┴ŽųąŻ¼┴¶Ž┬┴╦ę╗éĆĄų┐╣ļŖ┴„Ą─ļŖ║╔║─▒Mģ^ė“ĪŻ¼Fį┌Ą──┐ś╦╩Ū╩╣įōģ^ė“ūāĄ├╚ń┤╦╬ó▓╗ūŃĄ└Ż¼ęįų┴ė┌ļŖūė┐╔ęį║┴▓╗┘M┴”Ąž┤®▀^╦³ĪŻ

ĪĪĪĪį┌ų«Ū░Ą─蹊┐ųąŻ¼Įę╗ų▒╩Ū┼c MoS2ą╬│╔Š¦¾w╣▄Ą─*Įėė|▓─┴ŽĪŻĄ½│┴ĘeĮ║═Ųõ╦¹Ė▀╚█³cĮī┘Ģ■ōpē─Č■┴“╗»ŃfŻ¼╩╣ä▌ēŠ(barrier)å¢Ņ}ūāĄ├Ė³įŃĪŻ

ĪĪĪĪįńį┌2021─ĻĄ─IEDMŻ¼┼_ĘeļŖĄ─蹊┐╚╦åTŠ═ßśī”ųŲįņ 2D Š¦¾w╣▄ūŅ╝¼╩ųĄ─šŽĄKų«ę╗╠ß│÷┴╦å╬¬ÜĄ─ĮŌøQĘĮ░ĖŻ║░ļī¦¾wĮėė|╠ÄĄ─ļŖūĶ╝ŌĘÕĮī┘ė|³c(sharp spikes of resistance at the places where the semiconductor meets metal contacts)ĪŻČ°“õR”Š═╩Ū╦¹éāĄ─┤░ĖĪŻ

ĪĪĪĪ░┤šš┼_ĘeļŖŲ¾śI蹊┐▓┐Ą═ŠS蹊┐Įø└Ē Han Wang ĮķĮBŻ¼Š▀¾wū÷Ę©═©▀^╩╣ė├░ļĮī┘ū„×ķĮėė|▓─┴ŽüĒ£p╔┘░ļī¦¾w║═Įėė|ų«ķgĄ──▄ēŠ(energy barrier)ĪŻ░ļĮī┘(└²╚ńõR)Ą─ąą×ķŠ═Ž±╠Äė┌Įī┘║═░ļī¦¾wų«ķgĄ─▀ģĮń▓óŪęŠ▀ėą┴ŃĦŽČĪŻė╔┤╦«a╔·Ą─ąż╠ž╗∙ä▌ēŠĘŪ│ŻĄ═Ż¼╩ŪĄ─┼_ĘeļŖŲ„╝■Ą─ļŖūĶČ╝║▄Ą═ĪŻ

ĪĪĪĪ┼_ĘeļŖ┤╦Ū░į°┼c┴Ēę╗ĘN░ļĮī┘ŃG▀Mąą▀^║Žū„ĪŻĄ½Ųõ╚█³c╠½Ą═ĪŻ═§▒Ē╩ŠŻ¼õRŠ▀ėąĖ³║├Ą─¤ßĘĆČ©ąįŻ¼▀@ęŌ╬Čų°╦³īó┼c¼FėąąŠŲ¼ųŲįņ╣ż╦ćĖ³╝µ╚▌Ż¼Å─Č°╔·«a│÷Ė³─═ė├Ą─įOéõŻ¼▓ó×ķąŠŲ¼ųŲįņ╣ż╦ćĄ─║¾Ų┌╠ß╣®Ė³┤¾Ą─ņ`╗ŅąįĪŻ

ĪĪĪĪį┌▒Šī├Ą─IEDM ╔ŽŻ¼┼_ĘeļŖ╠ß│÷Ą─蹊┐ęįę╗ĘN╗“┴Ēę╗ĘNą╬╩ĮĮŌøQ┴╦╦∙ėą▀@╚²éĆå¢Ņ}ĪŻ

ĪĪĪĪ┼_ĘeļŖīóš╣╩Šīóę╗Ė∙Č■ŠS░ļī¦¾wĦČč»Bį┌┴Ēę╗Ė∙Ħ╔ŽĄ─蹊┐Ż¼ęįäōĮ©ŽÓ«öė┌ų¦│ųČ■ŠSĄ─╝{├ūŲ¼Š¦¾w╣▄ĪŻčąŠ┐╚╦åT▒Ē╩ŠŻ¼įōįOéõĄ─ąį─▄į┌ 2D 蹊┐ųą╩ŪŪ░╦∙╬┤ėąĄ─Ż¼Č°╚ĪĄ├▀@ę╗│╔╣¹Ą─ĻPµIį┌ė┌▓╔ė├┴╦ą┬Ą─Łh└@╩Įė|³cą╬ĀŅŻ¼Å─Č°ĮĄĄ═┴╦ļŖūĶĪŻ

ĪĪĪĪ╔ŽłD╩ŪČč»B 1L-MoS2 Ą─ (a) ┴┴ł÷ TEM łDŽ±║═ (b) ░Ął÷ TEM łDŽ±

ĪĪĪĪ┼_ĘeļŖ▒Ē╩ŠŻ¼─┐Ū░Ż¼╝{├ūŲ¼┐sĘ┼╩Ū═©▀^£p▒Ī╣Ķ═©Ą└üĒīŹ¼FĄ─Ż¼Ą½╬ęéā╚įį┌┼¼┴”īżšę╩╣ė├│¼▒Ī▀^Č╔Įī┘Č■┴“ī┘╗»╬’(TMD)ū„×ķ£ŽĄ└▓─┴ŽĄ─īŹė├ĘĮĘ©ĪŻ(MoS2Ą╚ TMD ▒╗ĘQ×ķå╬īė╗“ 2D ▓─┴ŽŻ¼ę“×ķ╦³éāų╗ėąįŁūėīė║±Č╚ĪŻ)

ĪĪĪĪ┼_ĘeļŖŅIī¦Ą─łFĻĀīóėæšōā╔éĆČč»B NMOS ╝{├ūŲ¼Ą─Ū░╦∙╬┤ėąĄ─ąį─▄Ż¼ŲõųąōĒėąMoS2¢┼śOķLČ╚Ą─ NMOS Ų„╝■▒Ē¼F│÷š²ķōųĄļŖē║(VTH~1.0V);Ė▀ī¦═©ļŖ┴„(IONon/off ratio (1E8);Ą═Įėė|ļŖūĶ(RC channelsĪŻVDS= 1V Ģr×ķ 40nm~370 µA/µm);┤¾~0.37-0.58 kΩ-µm)ĪŻ

ĪĪĪĪ▀@ą®ĮY╣¹Ą─ĻPµI╩Ūą┬ą═ C ą╬Łh└@Įėė|Ż¼╠ß╣®Ė³┤¾Ą─Įėė|├µĘe║═¢┼śOČč»Bā×╗»ĪŻ▀@ą®Ų„╝■▒Ē¼F│÷┐╔Įė╩▄Ą─ÖCąĄĘĆČ©ąįŻ¼Ą½čąŠ┐╚╦åT▒Ē╩ŠŻ¼ąĶę¬▀MąąĖ³ČÓ蹊┐üĒ£p╔┘ MoS2£ŽĄ└ųą╚▒Ž▌Ą─«a╔·ĪŻ

ĪĪĪĪ┼_ĘeļŖ▀Ćīóį┌▒Šī├IEDM╔ŽÄ¦üĒ*šµš²Ą─ 2D CMOS č▌╩ŠĪŻ

ĪĪĪĪō■ĮķĮBŻ¼Ųõ├┐éĆśOąįĄ─ FET Ų„╝■(n-FET ║═ p-FET)▒žĒÜ╠ß╣®Ųź┼õĄ─ąį─▄Ż¼ęį▒Ń CMOS ▀ē▌ŗŲ„╝■š²│Ż╣żū„ĪŻĄ½╩ŪŻ¼ļm╚╗ MoS2╩Ūę╗ĘN▀m║Ž n ą═Ų„╝■Ą─ TMD ▓─┴ŽŻ¼Ą½╦³▓╗▀mė├ė┌ p ą═Ų„╝■Ż¼Č° TMD ▓─┴Ž WSe2Ė³▀m║Ž p ą═Ų„╝■ĪŻ

ĪĪĪĪłD(a) ’@╩Š┴╦╦∙ųŲįņĄ─ n/p FET Ą─┴╝║├Ųź┼õĄ─▌ö│÷╠žąįĪŻłD(b) ╩ŪŠ▀ėą╣▓ą╬¢┼śOČč»BĄ─æęĖĪ MoS2 ╝{├ūŲ¼ĮYśŗĄ─ÖMĮž├µ TEMŻ¼įōĮYśŗ░³║¼ 10nm TiNĪó2nm HfOx ║═ 1 nm ILX(Įń├µļŖĮķ┘|)ĪŻ

ĪĪĪĪ┤╦═ŌŻ¼▀@ā╔ĘNśO▒ĪĄ─▓─┴ŽČ╝▒žĒÜūŃē“łį╣╠Ż¼─▄ē“│ą╩▄Ąõą═Ą─ųŲįņ╣ż╦ćĪŻTSMC ŅIī¦Ą─łFĻĀīóį┌śIĮń┬╩Ž╚├Ķ╩÷Ęųäe╩╣ė├▀@ā╔ĘN TMD £ŽĄ└▓─┴ŽųŲįņĄ─Ųź┼õ┴╝║├Ą─ n MOS Š¦¾w╣▄║═ p MOS Š¦¾w╣▄ĪŻ╦¹éā═©▀^į┌╦{īÜ╩»╔Žå╬¬Ü╔·ķL▀@ą®Ė▀│▀┤ń(~50nm £ŽĄ└ķLČ╚)║═Ė▀ļŖ┴„├▄Č╚▓─┴ŽŻ¼╚╗║¾īó╦³éāųéĆąŠŲ¼▐DęŲĄĮ 300mm ╣ĶŠ¦łA╔Ž▀Mąą╝»│╔Ż¼š╣╩Š┴╦▀@ą®▓─┴ŽĄ─¶ö░¶ąįĪŻ

ĪĪĪĪį┌┤╦▐DęŲ▀^│╠ų«║¾Ż¼Ų„╝■Ą─ąį─▄Äū║§ø]ėąĖ─ūāŻ¼n-FET ║═ p-FET (VDS = 1V) į┌ŽÓ═¼Ą─¢┼śO▀^“īäėŽ┬Š▀ėąĖ▀▌ö│÷ļŖ┴„ (~410 µA/µm)ĪŻ┤╦═ŌŻ¼p-FET ▀węŲ┬╩▀_ĄĮ┴╦Üv╩ĘūŅĖ▀╦«ŲĮ(~30 cm² /V∙s)ĪŻ

ĪĪĪĪ┴Ē▒┘§ĶÅĮĄ─ĮŌøQĘĮ░Ė

ĪĪĪĪIEEE▒Ē╩ŠŻ¼ÖCŲ„īW┴Ģųą*Ą─å¢Ņ}ų«ę╗╩ŪöĄō■Ą─ęŲäėĪŻ╔µ╝░Ą─ĻPµIöĄō■╩Ū╦∙ų^Ą─ÖÓųž║═╝ż╗ŅŻ¼╦³éāČ©┴xę╗īėųą╚╦╣ż╔±Įøį¬ų«ķgĄ─▀BĮėÅŖČ╚ęį╝░▀@ą®╔±Įøį¬īóé„▀fĄĮŽ┬ę╗īėĄ─ą┼ŽóĪŻ* GPU ║═Ųõ╦¹╚╦╣żųŪ─▄╝ė╦┘Ų„═©▀^╩╣öĄō■▒M┐╔─▄┐┐Į³╠Ä└Ēį¬╦žüĒā׎╚ĮŌøQ┤╦å¢Ņ}ĪŻčąŠ┐╚╦åTę╗ų▒į┌蹊┐ČÓĘNĘĮĘ©üĒū÷ĄĮ▀@ę╗³cŻ¼└²╚ńīóę╗ą®ėŗ╦Ń▐DęŲĄĮā╚┤µ▒Š╔Ēęį╝░īóā╚┤µį¬╦žČč»Bį┌ėŗ╦Ń▀ē▌ŗų«╔ŽĪŻ

ĪĪĪĪIEDM ūh│╠ųąĄ─ā╔éĆŪ░čž╩Š└²ę²Ų┴╦╬ęĄ─ūóęŌĪŻ*éĆ╩Ūīó─ŻöM AIė├ė┌╗∙ė┌ Transformer Ą─šZčį─Żą═(ChatGPTĄ╚)ĪŻį┌įōĘĮ░ĖųąŻ¼ÖÓųž▒╗ŠÄ┤a×ķļŖūĶ┤µā”į¬╝■(RRAM)ųąĄ─ļŖī¦ųĄĪŻRRAM ╩Ūł╠ąąĻPµIÖCŲ„īW┴Ģėŗ╦ŃĪó│╦Ę©║═└█╝ėĄ──ŻöMļŖ┬ĘĄ─ĮM│╔▓┐ĘųĪŻįōėŗ╦Ńęį─ŻöMĘĮ╩Į═Ļ│╔Ż¼ū„×ķļŖ┴„Ą─║åå╬Ū¾║═Ż¼┐╔─▄╣Ø╩Ī┤¾┴┐ļŖ┴”ĪŻ

ĪĪĪĪIBM Ą─ Geoff Burr į┌IEEE Spectrum 2021 ─Ļ 12 į┬╠¢╔Ž╔Ņ╚ļĮŌßī┴╦─ŻöM AI ĪŻį┌ IEDMŻ¼╦¹īó╠ß╣®ę╗ĘN─ŻöM AI ╠Ä└ĒTransformer ─Żą═Ą─įOėŗĪŻ

ĪĪĪĪIEDM ╔Ž│÷¼FĄ─┴Ēę╗éĆėą╚żĄ─╚╦╣żųŪ─▄ĘĮ░Ėį┤ūįŪÕ╚A┤¾īW║═▒▒Š®┤¾īWĄ─蹊┐╚╦åTĪŻ╦³╗∙ė┌╚²īėŽĄĮyŻ¼░³└©╣Ķ CMOS ▀ē▌ŗīėĪó╠╝╝{├ū╣▄Š¦¾w╣▄║═ RRAM īėŻ¼ęį╝░┴Ēę╗īėė╔▓╗═¼▓─┴ŽųŲ│╔Ą─ RRAMĪŻ╦¹éā▒Ē╩ŠŻ¼▀@ĘNĮM║ŽĮŌøQ┴╦įSČÓĘĮ░ĖųąĄ─öĄō■é„▌öŲ┐ŅiŻ¼▀@ą®ĘĮ░ĖįćłD═©▀^į┌ā╚┤µųąśŗĮ©ėŗ╦ŃüĒĮĄĄ═╚╦╣żųŪ─▄Ą─╣”║─║═čė▀tĪŻį┌£yįćųąŻ¼╦³ł╠ąą┴╦ś╦£╩łDŽ±ūRäe╚╬䚯¼ŲõŠ½Č╚┼c GPU ŽÓ╦ŲŻ¼Ą½╦┘Č╚┐ņ┴╦Į³ 50 ▒ČŻ¼─▄║─āH×ķ GPU Ą─ 1/40ĪŻ

ĪĪĪĪ╠žäe▓╗īż│ŻĄ─╩Ū╠╝╝{├ū╣▄Š¦¾w╣▄┼c RRAM Ą─ 3D Čč»BĪŻ├└ć°ć°Ę└Ė▀╝ē蹊┐ėŗäØŠų╗©┘MöĄ░┘╚f├└į¬īó▀@ĒŚ╝╝ągį┌ SkyWater Technology Foundry ķ_░l│╔╔╠śI┴„│╠ĪŻMax Shulaker ║═╦¹Ą─═¼╩┬į┌IEEE Spectrum 2016 ─Ļ 7 į┬╠¢╔ŽĮŌßī┴╦įō╝╝ągĄ─ėŗäØĪŻ╦¹Ą─łFĻĀė┌ 2019 ─Ļ└¹ė├įō╝╝ągśŗĮ©┴╦*éĆ 16 ╬╗┐╔ŠÄ│╠╝{├ū╣▄╠Ä└ĒŲ„ĪŻ

ĪĪĪĪ╬─š┬ā╚╚▌āH╣®ķåūxŻ¼▓╗śŗ│╔═Č┘YĮ©ūhŻ¼šłųö╔„ī”┤²ĪŻ═Č┘Yš▀ō■┤╦▓┘ū„Ż¼’LļUūįō·ĪŻ

║Żł¾╔·│╔ųą...

║Ż╦ćAIĄ──Żą═ŽĄĮyį┌ć°ļH╩ął÷╔ŽÅV╩▄║├įuŻ¼─┐Ū░šŠā╚└█ėŗ─Żą═öĄ│¼▀^80╚féĆŻ¼║Ł╔wīæīŹĪóČ■┤╬į¬Īó▓Õ«ŗĪóįOėŗĪóözė░Īó’LĖ±╗»łDŽ±Ą╚ČÓŅÉą═æ¬ė├ł÷Š░Ż¼╗∙▒ŠĖ▓╔w╦∙ėąų„┴„äōū„’LĖ±ĪŻ

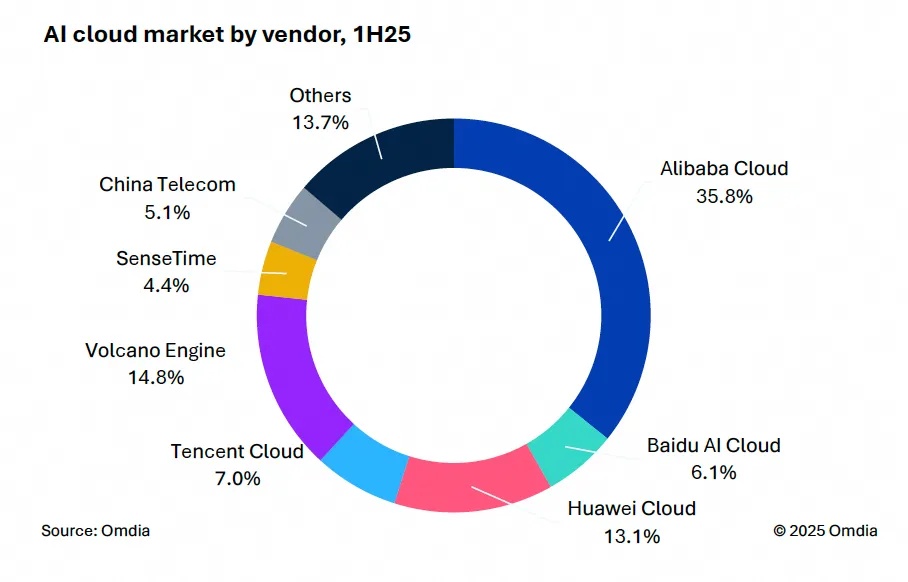

9į┬9╚šŻ¼ć°ļHÖÓ═■╩ął÷š{čąÖCśŗėóĖ╗┬³(Omdia)░l▓╝┴╦ĪČųąć°AIįŲ╩ął÷Ż¼1H25ĪĘł¾ĖµĪŻųąć°AIįŲ╩ął÷░ó└’įŲš╝▒╚8%╬╗┴ąĄ┌ę╗ĪŻ

9į┬24╚šŻ¼╚A×ķ└żņ`š┘ķ_Ī░ųŪ─▄¾w“ׯ¼ę╗Ų┴ĄĮ╬╗Ī▒╚A×ķIdeaHubŪ¦ąą░┘śI¾w“×╣┘ėŗäØ░l▓╝Ģ■ĪŻ

č┼±R╣■ū“╚šą¹▓╝═Ų│÷ā╔┐ŅŅ^┤„╩ĮČ·ÖCŻ¼Ęųäe╩ŪŲĮ░Õš±─żĄ─YH-4000║═äė╚”įŁ└ĒĄ─YH-C3000ĪŻ

IDCĮ±╚š░l▓╝Ą─ĪČ╚½Ū“ųŪ─▄╝ęŠėŪÕØŹÖCŲ„╚╦įOéõ╩ął÷╝ŠČ╚Ė·█Öł¾ĖµŻ¼2025─ĻĄ┌Č■╝ŠČ╚ĪĘ’@╩ŠŻ¼╔Ž░ļ─Ļ╚½Ū“ųŪ─▄╝ęŠėŪÕØŹÖCŲ„╚╦╩ął÷│÷žø1,2╚f┼_Ż¼═¼▒╚į÷ķL33%Ż¼’@╩Š│÷ŲĘŅÉÅŖä┼Ą─╩ął÷ąĶŪ¾ĪŻ